- Logicworks 5 interactive circuit design software how to#

- Logicworks 5 interactive circuit design software Pc#

Lab sessions take place in either the PC classroom or in a conventional classroom. Students acquire with the knowledge needed to make an early start on the practical work. The first four weeks of the course stress theory classes, and include some tasks. The course stresses putting theory into practice. Furthermore, the teacher will prevent over-simplified implementation being adopted to ensure that the whole process is as realistic as possible. Students tackle a real project in which the various groups have to communicate with one another and reach agreement on an implementation that is straightforward for all concerned. It goes without saying that this form of learning is both extremely effective and highly motivating. In other words, students will work in groups and by stages but must assemble all of the processor components to produce a working whole. It should be stressed that all students will work on the same processor. The processor must include a cache hierarchy (instructions and data), and must share data with a disk controller through a bus and main memory. Students will collectively undertake a practical session involving implementing a simple 5, 6, or 7-stage multi-cyclic, superscalar processor incorporating jump prediction. Theory and Problems: Common problems (lecture) Introduction to the architecture of current processors. Assume responsibility for one"s own work.Ability to understand and constructively criticise presentations given by others.Ability to set up and organise either a uni- or multi-disciplinary group to tackle a complex project.Ability to work effectively in large groups to solve complex problems.

Logicworks 5 interactive circuit design software how to#

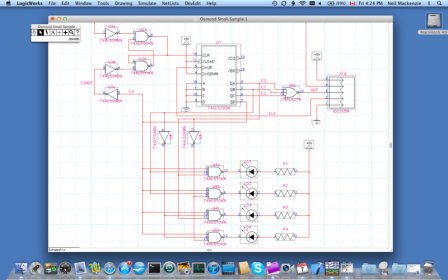

Ability to create and use models of reality.Ability to solve problems through the application of scientific and engineering methods.Use verilog as a hardware modelling language in order to model the processors presented in class.Ability to create a model of the processors presented and simulate their operation. Mastery of LogicWorks 4 and LogicWorks 5 simulators.Example of the workings of a 3D graphic processor. The concept behind specific purpose processors: embedded, DSP, and 3D graphic processors.Specific memory access instructions (Strides and Gather/Scatter). Advantages and drawbacks of vectorial execution. Incorporating two threads for renaming in an out-of-order segmented pipeline. Types of multithreading: fine-grain, switch-on-event, simultaneous multithreading. Prerequisites for simultaneously executing two instructions. Fetching multiple instructions within a clock cycle. Control dependencies among memory instructions. Selection (pick & wake-up) of instructions within an instruction window.

Recovering the rename table in cases of exception. Recovering Precise State in cases of exception and interruption. Re-order Buffer and Future File technique (Smith & Plezskun, 1985). Out-of-order execution ("complete out of order" and "initiate and complete out of order" variants).Integration of the predictor in the segmented pipeline. Two-bit predictors with history registers. The impact of exceptions and interruptions in the segmentation process. TLB (translation look-aside buffer) concept, Operating System support for virtual paging memory, and fault management in the TLB.Store-load dependencies in a pipeline with two write stages. Memory hierarchy, store instruction ordering, write-to-cache techniques, write buffer, merge buffer, cache flush.

0 kommentar(er)

0 kommentar(er)